全球首家?这家代工厂官宣生产3纳米芯片,磐矽半导体/高通或首发

电子芯片网消息,近日,韩国半导体厂商三星抢先晶圆代工龙头台积电,量产3纳米的消息引发业界高度关注。最新消息是,三星已经正式官宣量产3纳米芯片的消息。

今日(6月30日),三星通过其微信公众号“三星半导体和显示官方”宣布,基于3nm全环绕栅极(Gate-All-AroundT,简称GAA)制程工艺节点的芯片已经开始初步生产,首先将应用于高性能、低功耗计算领域的半导体芯片,并计划将其扩大至移动处理器领域。

与三星5nm工艺相比,三星第一代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;三星表示,未来第二代3nm工艺将使功耗降低50%,性能提升30%,芯片面积减少35%。

至于3纳米客户方面,有媒体报道称,消息人士透露,三星称已经有客户订购产能,包括虚拟货币挖矿机芯片设计公司上海磐矽半导体 (PanSemi),以及移动处理器大厂高通 (Qualcomm) 等,不过高通将视情况进行投片。

从时间节点来看,三星3纳米技术量产时间确实领先台积电。

根据台积电近期在技术研讨会北美专场分享的制程技术发展蓝图及未来计划,其初始3纳米节点(N3)有望于今年下半年开始量产,并从明年初交付给客户。此外,台积电未来几年还将推出多种N3衍生制造工艺。

2纳米制程工艺方面,台积电透露,N2工艺节点将首次使用GAAFET架构,计划在2025年投产。

(本文内容信息不代表电子芯片网观点,如有版权疑问请马上联系客服。)

芯片头条

-

全球加速碳化硅产能扩充

2024-03-20 -

ASML推出全新Hyper-NA EUV技术,预计2030年问世引领半导体新篇章

2024-02-28 -

麒麟9000S供应问题即将解决!华为手机24年冲击1亿部!

2024-01-08 -

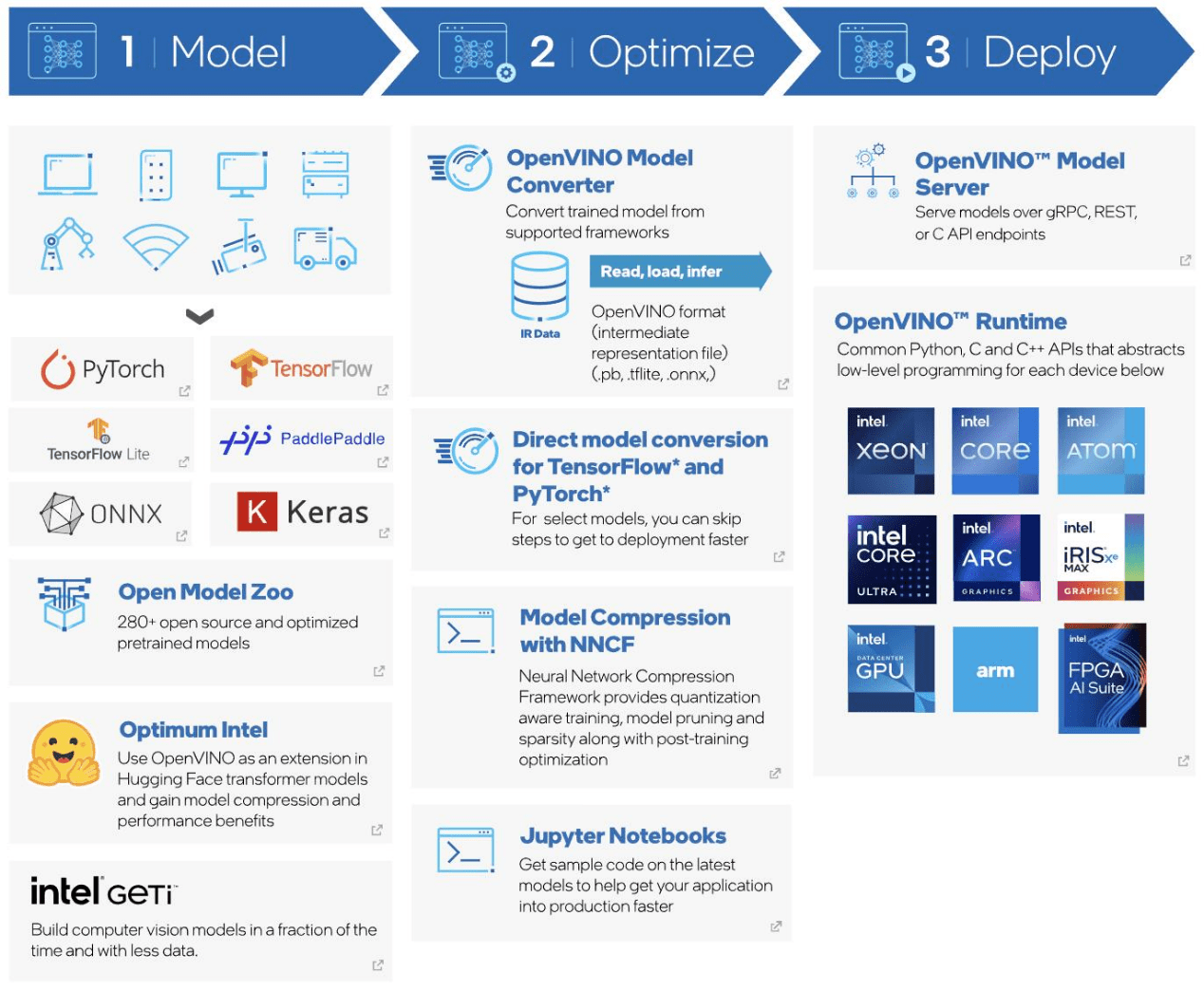

为AI加速而生 英特尔CPU能跑200亿参数大模型

2023-12-22 -

Gartner预测2024年全球半导体市场回暖,收入将达6240 亿美元

2023-12-06